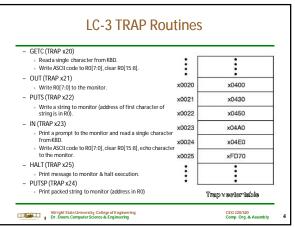

| 01   |            | ORIG      | X0430       | ; System call starting address |

|------|------------|-----------|-------------|--------------------------------|

| 02   |            | ST        | R1, SaveR1  | ; R1 will be used for polling  |

| 03   |            | •.        | ni, our oni | , it in be about of poining    |

| 04   | : Write th | ne charao | ter         |                                |

| 05   | TryWrite   | LDI       | R1. DSR     | : Get status                   |

| 06   |            | BRzp      | TryWrite    | ; bit 15 = 1 => display ready  |

| 07   | Writelt    | STI       | RÓ, DDR     | Write character in R0          |

| 08   |            |           |             |                                |

| 09   | ; Return   | from TR/  | AP          |                                |

| 0A   | Return     | LD        | R1, SaveR1  | ; Restore registers            |

| 0B   |            | RET       |             | ; Return (actually JMP R7)     |

| 0C   | DSR        | .FILL     | xFE04       | ; display status register      |

| 0D   | DDR        | .FILL     | xFE06       | ; display data register        |

| 0E   | SaveR1     |           | 1           |                                |

| 0F   |            | .END      |             |                                |

| ALSO |            |           |             |                                |

| 01   |            | ORIG      | x0021       |                                |

| 02   |            | FILL      | x0430       |                                |

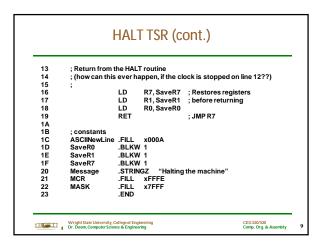

|    |              | HALT TS           | DR                              |

|----|--------------|-------------------|---------------------------------|

|    |              |                   |                                 |

|    | RUN latch MC |                   |                                 |

| 01 | .ORIG        | XFD70             | ; System call starting address  |

| 02 | ST           | R0, SaveR0        | ; Saves registers affected      |

| 03 | ST           | R1, SaveR1        | ; by routine                    |

| 04 | ST           | R7, SaveR7        | ;                               |

| 05 |              |                   |                                 |

|    |              | that machine is h |                                 |

| 07 | LD           | R0, ASCIINewL     | ine                             |

| 08 | TRAP         | x21               | ; Set cursor to new line        |

| 09 | LEA          | R0, Message       | ; Get start of message          |

| 0A | TRAP         | x22               | ; and write it to monitor       |

| 0B | LD           | R0, ASCIINewL     | ine                             |

| 0C | TRAP         | x21               |                                 |

| 0D |              |                   |                                 |

|    |              | o stop the clock  |                                 |

| 0F | LDI          | R1, MCR           | ; Load MC register to R1        |

| 10 | LD           | R0, MASK          | ; MASK = x7FFF (i.e. bit 15 = 0 |

| 11 | AND          | R0, R1, R0        | ; Clear bit 15 of copy of MCR   |

| 12 | STI          | R0, MCR           | ; and load it back to MCR       |

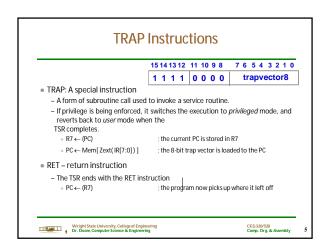

| A = IR[11] specifies                        | 15141312 11 10 9 8 7 6 5 4 3 2 1 0                           |

|---------------------------------------------|--------------------------------------------------------------|

| the addressing mode                         | 0 1 0 0 1 Address eval. bits                                 |

| JSR: jump to subroutine (PC-<br>- R7 ← (PC) | JSR(R) A<br>-Relative), IR[11] = 1<br>i.e. PC is saved to R7 |

| ( )                                         | i.e PC-Relative addressing,                                  |

| .,,                                         | e within +1024 / -1023 lines of JSR instruction              |

|                                             | 15141312 11 10 9 8 7 6 5 4 3 2 1                             |

|                                             | 01000 BaseR 00000                                            |

| JSRR: jump to subroutine (re                | JSR(R) A<br>elative base+offset), IR[11] = 0:                |

| – R7 ← (PC) i.e. F                          | PC is saved to R7                                            |

|                                             |                                                              |

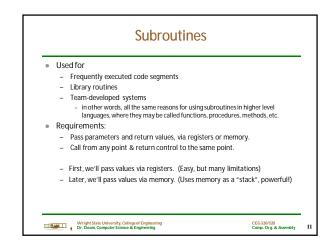

| Colling                          | program |                               | ; Subrou  | itine multi |                    |

|----------------------------------|---------|-------------------------------|-----------|-------------|--------------------|

| ; Calling program<br>.ORIG x3000 |         | ; Multiply 2 positive numbers |           |             |                    |

|                                  |         | ; Parameters:                 |           |             |                    |

|                                  | LD      | R1, num1                      | ; In: R1, | R2; Out: R  | 23                 |

|                                  | LD      | R2, num2                      | ;         |             |                    |

|                                  | JSR     | multi                         | multi     | AND         | R3, R3, #0         |

|                                  | ST      | R3, prod                      |           | ADD         | R4, R1, #0         |

|                                  | HALT    |                               |           | BRz         | zero               |

| ;                                |         |                               | loop      | ADD         | R3, R2, R3         |

| ; Input data & result            |         |                               |           | ADD         | R1, R1, # -1       |

| num1                             | FILL    | x0006                         |           | BRp         | loop               |

| num2                             | FILL    | x0003                         | zero      | RET         |                    |

|                                  |         |                               |           | .END        |                    |

| prod                             | .BLKW   | 1                             |           |             | able side-effects? |

| Practice Problem                                                                            | IS                                      |

|---------------------------------------------------------------------------------------------|-----------------------------------------|

| <ul><li>9.2, 9.7, 9.10, 9.13, 9.15</li></ul>                                                |                                         |

|                                                                                             |                                         |

|                                                                                             |                                         |

|                                                                                             |                                         |

| Wright State University, College of Engineering<br>Dr. Doom, Computer Science & Engineering | CEG 320/520<br>Comp. Org. & Assembly 17 |